# Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb Junctions with Inductive Tuning Elements for a Very Low Noise 205–250 GHz Heterodyne Receiver

Arthur W. Lichtenberger, Dallas M. Lea, *Student Member, IEEE*, Robert J. Mattauch, *Fellow, IEEE*, and Frances L. Lloyd

**Abstract**—The superconductor-insulator-superconductor (SIS) junction is the most sensitive nonlinear element for millimeter-wave heterodyne detection. We have developed a Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb junction fabrication process which allows the use of planar tuning circuits integrated with the junctions. These tuning elements permit the use of junctions with relatively large areas and small current densities with excellent results. Recent measurements have yielded a double sideband receiver noise temperature less than 50K from 205 to 240 GHz and 44K at 230 GHz. We are also extending our Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb trilayer technology to the fabrication of sub-square-micron area planar junctions for submillimeter wavelengths.

## I. INTRODUCTION

Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb trilayer junctions have surpassed those made by all other SIS technologies in leakage current and uniformity. They are currently the element of choice for ultra low noise millimeter wave heterodyne detection. We are investigating both Nb and NbCN superconductors in the planar and edge junction geometries for millimeter and submillimeter wavelengths. In this paper we discuss the recent results of our Nb trilayer technology.

There have generally been two approaches to optimizing SIS mixers for millimeter wavelengths: 1) the use of very small area, high current density ( $J_c$ ) junctions to minimize  $\omega R_N C$  [1]–[5], where  $R_N$  is the normal state resistance and  $C$  is the junction capacitance, and 2) the use of integrated elements to tune out the junction capacitance while keeping the benefits of a larger junction capacitance [6]–[11]. For millimeter wavelength, both approaches have been rather successful. At higher frequencies the use of increasingly smaller junction areas and higher  $J_c$  values may be restricted by fabrication limitations and the properties of available superconductors. For example, with  $C_s = 45 \text{ fF}/\mu\text{m}^2$ ,  $I_C R_N = 1.8 \text{ mV}$ , and  $R_N = 100 \Omega$  [12], a choice of  $\omega R_N C = 1$  at 100 GHz with the Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb system requires a junction area of approxi-

mately  $0.35 \mu\text{m}^2$  and a  $J_c = 5.1 \times 10^3 \text{ A}/\text{cm}^2$ . Even if we ignore the  $J_c \propto f^2$  relationship found by Kerr and Pan for the choice of  $\omega R_N C = 4$  [10], at 600 GHz and 1 THz the desired junction areas and  $J_c$  values would still be  $0.06 \mu\text{m}^2$  and  $3 \times 10^4 \text{ A}/\text{cm}^2$ , and  $0.035 \mu\text{m}^2$  and  $5 \times 10^4 \text{ A}/\text{cm}^2$ , respectively. In light of the analysis by Kerr and Pan, these numbers, particularly the  $J_c$  values, are certainly optimistic estimates. The fabrication of such planar trilayer junctions having reasonable electrical characteristics may be quite difficult. An attractive alternative is the use of integrated superconductive tuning elements and impedance matching superconductive transmission lines, which permit the use of larger junction areas and smaller  $J_c$  values (larger  $\omega R_N C$ ). Additionally, the expected difficulty in suppressing Josephson currents (and the resulting Josephson noise) for very small junction areas and arrays of junctions argues for the integrated tuning element approach. Resistive loss in superconductor films at frequencies approaching  $2\Delta/h$  ( $\approx 700 \text{ GHz}$  for Nb) will, however, prevent the use of superconductive tuning elements above these frequencies, and normal metal tuning elements [9] or alternative mixer designs will need to be developed.

## II. SIS MIXER ELEMENTS WITH INTEGRATED TUNING ELEMENTS

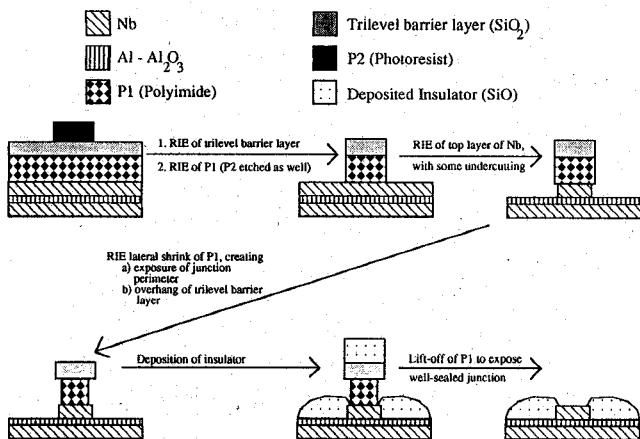

For SIS mixers, the use of relatively large  $\omega R_N C$  values has three advantages: (i) The large capacitance tends to short-circuit currents at the LO harmonics and harmonic sidebands, (ii) Undesired effects of the AC Josephson currents in the junction are reduced, and (iii) It is easier to fabricate the required junction elements. However, for good mixer performance it is necessary to tune out the junction capacitance at the signal frequency. To do this, we have used inductive tuning circuits integrated with the individual junctions [9], [12], [13]. In our earlier work [9], [13], we reported utilizing a trilevel resist to pattern junction areas in Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb films and to define the inductive portion of the stripline tuning element (Fig. 1). After reactive ion etching to define the junction area, the perimeter of the junction is revealed and a liftoff structure is defined with an oxygen plasma shrink of the exposed polyimide sidewalls. A subsequently off-axis de-

Manuscript received May 14, 1991; revised December 30, 1991. This work was supported in part by the National Aeronautic and Space Administration under Grant No. NAGW-2377, and the National Science Foundation under Grant No. AST8922155.

The authors are with the Department of Electrical Engineering, University of Virginia, Charlottesville, VA 22903.

IEEE Log Number 9106970.

Fig. 1. Outline of original trilevel resist insulation process.

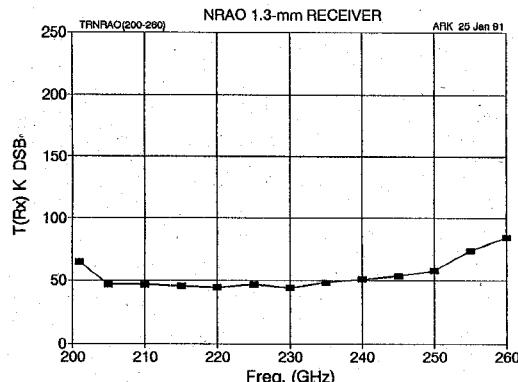

Fig. 2. Noise temperature measurements from 205 GHz to 260 GHz for a NRAO receiver incorporating Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb junctions fabricated at the University of Virginia. The DSB receiver noise temperature at 230 GHz was 44K.

posited insulation layer seals the sides and the perimeter of the Nb counter electrode button and forms the dielectric for the inductive superconductive stripline. The excellent liftoff profile that is obtained with this technique allows the use of thick insulation layers. We have utilized this technique repeatedly to fabricate high-quality junctions of  $1.5 \mu\text{m}$  diameter and current density as large as  $1 \times 10^4 \text{ A/cm}^2$ .

The most recent results at 230 GHz are shown in Fig. 2. A six junction array was mounted in an NRAO-401 mixer which utilizes two non-contacting adjustable tuners positioned in full-height waveguide. The DSB mixer noise temperature and gain at 230 GHz are 15.5K and  $-1.5 \text{ dB}$  respectively. The receiver has a DSB noise temperature ( $T_R$ ) of 44 K at 230 GHz, and a  $T_R$  below 50K from 205 GHz to 240 GHz [14]. These figures are the lowest reported for a receiver operating over this frequency range. The integrated tuning elements permitted the use of junctions which are relatively large ( $A \approx 4 \mu\text{m}^2$ ) and also have a low current density ( $J_c \approx 3 \times 10^3 \text{ A/cm}^2$ ).

### III. Cr TRILEVEL RESIST INSULATION PROCESS

The optimal performance of SIS mixers requires that the junction area be decreased as the frequency of oper-

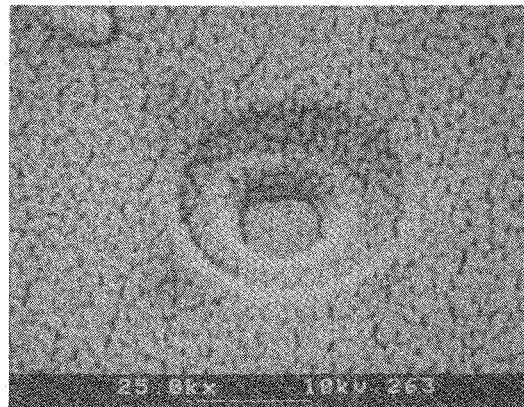

ation increases; however, an isotropic Nb etch limits the present SiO<sub>2</sub> trilevel process to the fabrication of junctions with an area of  $\approx 1.5 \mu\text{m}^2$ . The limitation arises from an unfortunate characteristic of the SiO<sub>2</sub> masking layer: it etches rapidly in low pressure CF<sub>4</sub> based etches which are otherwise well-suited for anisotropic definition of the Nb counter electrode. The high pressure (300  $\mu\text{m}$ ) Nb etch of the present process appreciably increases lateral etching, or "undercutting," of the Nb counter electrode. The undercutting is especially problematic for small features because the Nb counter electrode is either etched away entirely or is so small that the subsequent oxygen plasma shrink of the polyimide layer to expose the counter electrode perimeter can not be performed repeatably, (Fig. 3).

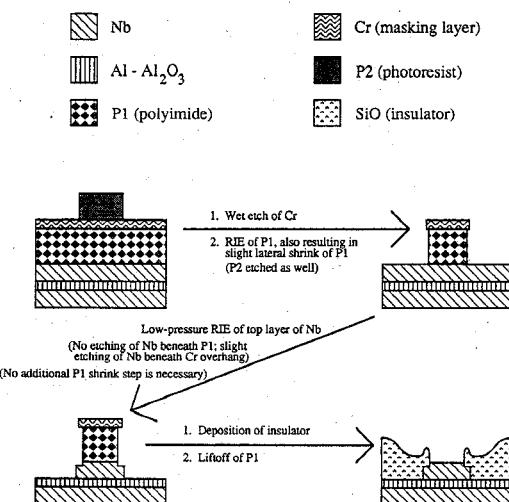

Our new approach involves the replacement of the SiO<sub>2</sub> with a  $\approx 600 \text{ \AA}$  Cr layer (defined by wet etching) which is resistant to the CF<sub>4</sub> + O<sub>2</sub> Reactive Ion Etching (RIE) chemistry. As a result, the Nb counter electrode layer may be etched with a low pressure (25  $\mu\text{m}$ ) RIE process which yields no undercutting. In fact, we have determined that if the polyimide features are shrunk *prior* to the low pressure Nb etch, then the Nb etch defines junctions whose sizes are determined by the Cr overhang of each feature rather than by the polyimide. The low pressure etch leaves the Nb untouched beneath the polyimide and only slightly etches the Nb beneath the Cr overhang. Consequently, there is already an exposed top surface along the perimeter of each junction, so no additional polyimide shrink step is necessary before the deposition of the SiO insulation layer. Eliminating the polyimide shrink after the Nb etch is particularly beneficial because difficulties in shrinkage due to Plasma Resist Image Stabilization Technique (PRIST) hardening [9], [15] from the Nb etch are avoided.

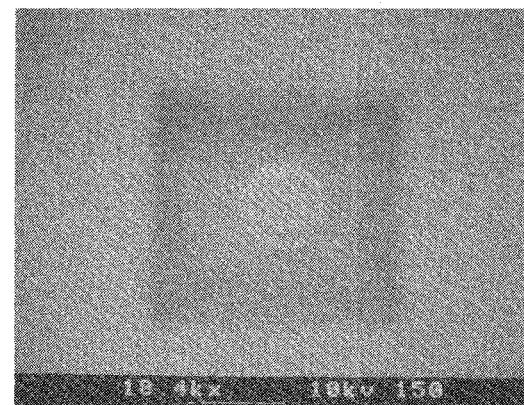

This improved approach is depicted in Fig. 4; it should be noted that the polyimide defining etch and polyimide shrink have been combined into a single step. These were combined by decreasing the power density and hence the anisotropy of the initial polyimide etch. Fig. 5 is an SEM micrograph of a 1  $\mu\text{m}$  diameter junction prior to insulator deposition and polyimide liftoff. It is apparent that there is enough exposed area along the perimeter to easily allow sealing of the junction perimeter with an insulator. Fig. 6 shows such a sealed junction after the polyimide liftoff. If wafers were kept stationary during the off-axis deposition of SiO, the Cr overhang would prevent SiO from reaching a portion of each junction perimeter. Thus, in order to allow symmetric coverage of the junction perimeters, the wafer is rotated, resulting in the ring of thinner SiO surrounding each junction.

In Fig. 7, the deposition of SiO has been omitted; however, the polyimide feature has been lifted off to expose an entire junction. In addition to allowing an accurate determination of junction size, such a view also clearly indicates a slight etching of the Nb which was outside the polyimide feature yet beneath the Cr overhang. When the SiO deposition step is included before liftoff, the SiO covers this ring of slightly etched Nb (Fig. 4). Our results

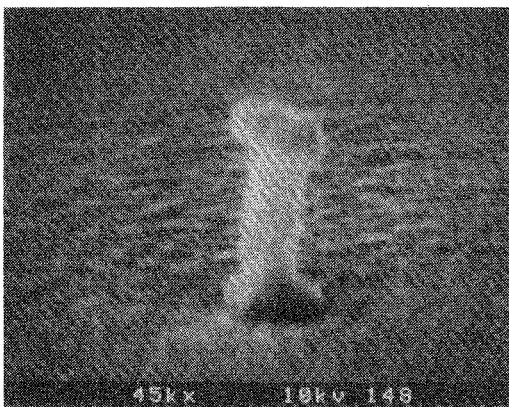

Fig. 3. An SEM micrograph of a  $0.3 \mu\text{m} \times 0.3 \mu\text{m}$  Nb junction area for which a successful  $\text{SiO}_2$  based trilevel resist feature was obtained. The shrinkage from the mask feature size of  $0.8 \mu\text{m} \times 0.8 \mu\text{m}$  is primarily due to the "undercutting" of the Nb film in the high pressure  $\text{CF}_4 + \text{O}_2$  etch. A lateral shrinkage of  $0.25 \mu\text{m} < x_{\text{shrink}} < 0.35 \mu\text{m}$  was therefore required for this successful polyimide shrink step. This step is performed, however, without quantitative information on the extent of the Nb undercutting, resulting in poor repeatability.

Fig. 4. Improved trilevel resist process featuring CR masking layer.

Fig. 5. An SEM micrograph of a Cr based trilevel resist defined Nb counter electrode. The excellent lift-off profile has been obtained with a pre-shrink of the polyimide *prior* to definition of the junction area. The subsequent  $\text{SiO}$  deposition will insulate the perimeter of the junction area.

Fig. 6. An SEM micrograph of a Nb counter electrode whose perimeter has been well sealed with  $\text{SiO}$  using the improved trilevel resist process. (The cracks are in a gold layer deposited on the SEM sample to create a conducting surface.)

Fig. 7. An SEM micrograph of a  $1 \mu\text{m}$  diameter Nb electrode on a wafer for which the  $\text{SiO}$  insulation step was omitted.

indicate that the width of this ring varies very little with junction size; thus, junctions of a wide range of sizes should be equally well-sealed along their perimeters. Presently, we have used this Cr-based trilevel resist process to define junction areas as small as  $0.5 \mu\text{m}^2$ .

#### IV. SUMMARY

SIS mixer elements, based on the Nb/Al trilayer system, have resulted in very low receiver noise temperatures from 205 GHz to 240 GHz. Although other material systems and geometries (the NbN/MgO material system and the edge geometry in particular) appear attractive for submillimeter wavelengths, the Nb/Al trilayer system may prove to be a competitive technology. Our present research with the Nb trilayer system includes new fabrication techniques for sub-square-micron junction areas, and individually tuned and fixed tuned SIS detector elements. In addition to heterodyne detection work, direct detection experiments are ongoing at 585 GHz and 763 GHz.

#### ACKNOWLEDGMENT

The authors gratefully acknowledge the vital contributions to this work by S.-K. Pan, A. R. Kerr, and A. C. Hicks.

## REFERENCES

- [1] T. G. Phillips and D. P. Woody, *Annu. Rev. Astron. Astrophys.*, vol. 20, p. 285, 1982.

- [2] J. Ibruegger, K. Okuyama, R. Blundell, K. H. Gundlach, and E. J. Blum, in *Proc. 17th Int. Conf. on Low Temperature Physics*, p. 937, 1984.

- [3] D. W. Face, D. E. Prober, W. R. McGrath, and P. L. Richards, "High quality tantalum superconducting tunnel junctions for microwave mixing in the quantum limit," *Appl. Phys. Lett.*, vol. 48, no. 16, p. 1098, 1986.

- [4] H. H. S. Javadi, W. R. McGrath, S. R. Cypher, B. Bumble, B. D. Hunt, and H. G. LeDuc, "Performance of SIS mixers at 205 GHz employing submicron Nb and NbN tunnel junctions," in *Proc. 15th Int. Conf. on Infrared and Millimeter Waves*, 1990.

- [5] D. P. Woody, C. J. Giovanine, and R. E. Miller, "Dual channel 115 and 230 GHz SIS receivers in operation at the Owens Valley Radio Observatory," *IEEE Trans. Magn.*, vol. 25, no. 2, pp. 1366-1370, 1989.

- [6] L. R. D'Addario, "An SIS mixer for 90-120 GHz with gain and wide bandwidth," *Int. J. Infrared and Millimeter Waves*, vol. 5, no. 11, p. 1419, 1984.

- [7] A. V. Raisanen, W. R. McGrath, P. L. Richards and F. L. Lloyd, "Broadband RF match to a millimeter-wave SIS quasi-particle mixer," *IEEE Trans. Microwave Theory Tech.*, vol. 33, no. 12, p. 1495, 1985.

- [8] A. R. Kerr, S.-K. Pan, and M. J. Feldman, "Integrated tuning elements for SIS mixers," *Int. J. Infrared and Millimeter Waves*, vol. 9, no. 2, p. 203, 1988. This paper was presented at the *Int. Superconductivity Electronics Conf.*, Tokyo, Japan, 1987.

- [9] A. W. Lichtenberger, D. M. Lea, C. Li, F. L. Lloyd, R. J. Mattauch, M. J. Feldman, S.-K. Pan, and A. R. Kerr, "Fabrication of micron size artificially insulated Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb junctions with a trilevel resist lift-off process," *IEEE Trans. Magn.*, vol. 27, no. 2, pp. 3168-3171, 1991.

- [10] A. R. Kerr and S.-K. Pan, "Some recent developments in the design of SIS mixers," in *Proc. First Int. Symp. on Space Terahertz Technology*, 1990, pp. 363-376.

- [11] D. Winkler, A. H. Worsham, N. G. Ugrass, D. E. Prober, N. R. Erikson, and P. F. Goldsmith, "A 75-110 GHz SIS mixer with integrated tuning and coupled gain," *Nonlinear Superconductive Electronics and Josephson Devices*, 1991.

- [12] A. W. Lichtenberger, C. P. McClay, R. J. Mattauch, M. J. Feldman, S. K. Pan, and A. R. Kerr, "Fabrication of Nb/Al-Al<sub>2</sub>O<sub>3</sub>/Nb Junctions with Extremely Low Leakage Currents," *IEEE Trans. Magn.*, vol. 25, pp. 1247-1250, 1989.

- [13] R. J. Mattauch, W. L. Bishop, and A. W. Lichtenberger, "Recent results on: Surface-channel Schottky, InGaAs Schottky, and Nb based SIS mixer element research," in *Proc. First Int. Symp. Space Terahertz Technology*, Mar. 1990, pp. 273-292.

- [14] S.-K. Pan and A. R. Kerr, National Radio Astronomy Observatory, private communication, Jan. 1991.

- [15] W. H-L. Ma, *Proc. SPIE Submicron Lithography*, vol. 33, pp. 12-23, 1982.

**Arthur W. Lichtenberger** was born in Westfield, NJ on April 22, 1958. He received the B.A. degree in physics from Amherst College in 1980, and the M.S. and Ph.D. degrees in electrical engineering from the University of Virginia in 1985 and 1987, respectively.

Dr. Lichtenberger joined the Faculty at the University of Virginia in 1987 as an Assistant Research Professor. He is currently directing the research on superconducting detector elements in the Semiconductor Device Laboratory.

He is a member of Sigma Xi and Tau Beta Pi.

Kappa Nu.

**Dallas M. Lea** (S'88) was born in Morgantown, WV on December 3, 1966. He received the B.S. and M.S. degrees in electrical engineering from the University of Virginia in a combined program in 1990. He is currently pursuing the Ph.D. degree at the University of Virginia, where his research focuses on the fabrication and testing of high-frequency superconducting devices. In 1991, he was awarded a NASA Graduate Student Researchers Program fellowship.

Mr. Lea is a member of Tau Beta Pi and Eta

**Robert J. Mattauch** (S'61-M'66-SM'81-F'86) received the B.S.E.E. degree from the Carnegie Institute of Technology in 1962 and the M.E.E. and Ph.D. degrees in electrical engineering from North Carolina State University, Raleigh, in 1963 and 1967, respectively. He was a Ford Fellow at North Carolina State University.

His research interests lie in the area of semiconductor materials and devices, with specific emphasis on III-V compounds and millimeter-wave structures. He is presently the BP America

Professor of Electrical Engineering at the University of Virginia, Charlottesville.

Dr. Mattauch is the founder of the Semiconductor Device Laboratory at the University of Virginia, and was elected Fellow of the IEEE for contributions to the development of low-noise millimeter-wave diode technology. He is a member of Eta Kappa Nu, Sigma Xi, Phi Kappa Phi, and Tau Beta Pi.

**Frances L. Lloyd** (nee Frances L. Lummis) received the B.S. degree from Duke University in 1946 and the M.S. degree from the University of Virginia in 1948, both in physics.

She joined the staff at the Naval Ordnance (now Naval Surface Weapons) Laboratory in White Oak, MD and worked in the Solid State Division for ten years before leaving to be married. In 1977, Mrs. Lloyd joined the Cryoelectronic Metrology Group at the National Bureau of Standards (now National Institute of Standards and Technology) in Boulder, CO. In 1989, she retired from the government and accepted a half-time position as a senior scientist with the Department of Electrical Engineering at the University of Virginia, where she continues to work on the fabrication of superconducting circuits.